新芯片技术全面靠拢AI!

共 1 个回答

Google开始尝试以机器学习(ML)在IC设计中执行布局与绕线(place-and-route),并正逐渐取得不错的成果。在日前于美国加州举行的国际固态电路研讨会(ISSCC)上揭露的这一事实,无论对于电路设计还是人工智能(AI)都是同样重要的。

多年来,AI一直是电子产业中的头号大事,这一发展方向(伴随创投与头条新闻)也不断吸引着大量的半导体研究。因此,今年的ISSCC主题很自然的就订为“IC技术启动AI时代”(Integrated

Circuits Powering the AI Era),而一开幕的大会议程也在致力于描绘AI如何改写整个半导体样貌。

开场会议的几位发言人解释了AI的具体需求,例如,驱动专为AI应用而设计的新型处理器(以及CPU和GPU);促进结构创新,包括小芯片(chiplets)、多芯片封装与中介层;甚至是影响着量子运算的发展。

大会的第一位发言人是Google AI负责人Jeff Dean,他简介了机器学习的最新内容。过去一年多以来,Dean持续以各种形式发表演讲,引导产业针对ML布局与绕线工具的更多讨论。

比较针对布局与绕线ASIC设计的专家经验与低功耗ML加速芯片的结果。但Google故意遮掉了部分影像…(来源:Google Research/ISSCC)

他首先简要介绍AI和ML的历史,从1995年机器如何学习玩西洋棋开始,到让机器学会在棋赛中脱颖而出,现在已经可以在《星海争霸》(StarCraft)等复杂的视讯游戏取得斐然成绩。ML还被用于医学成像、机器人技术、计算机视觉、自动驾驶车、神经科学、农业以及天气预报等领域。

数十年来推动运算发展的基本思维是,问题越大,需要的处理能力就越强大,而拥有的处理能力越强,所能解决的问题就越重大。长久以来,这一概念都适用于以AI解决种种问题。

而当问题的领域日益扩展到过于广泛而无法解决时,根本就不可能再光靠聚集更多CPU(和/或GPU)的能力来解决。

而AI/ML则不需要典型的CPU/GPU能力。其所需的数学运算可能更简单,而所要求的精度则要低得多。对于这一类应用的了解带来了实际的影响:专用于AI/ML的处理器并不必像CPU/GPU那样复杂。

这是导致专用处理器为推论而生的看法之一。例如Google TensorFlow,如今已发展到第三代了。尽管普遍预期Google不久将推出第四代TensorFlow,但如果您指望在今年ISSCC上透露任何相关信息的话,希望可就破灭了。

除了推论所需的精度较低之外,业界也发现“训练”(training)的精度要求也较低些——这是相对较新的发现。AI/ML处理器可能相对较简单,因而也较便宜,而且,目前的AI/ML处理器即使用于大量数据集上,也有足够强大的能力进行快速训练。Dean解释,这些都让ML更易于进一步推向网络边缘,例如语音识别应用。2019年,Google曾为此开发一款可执行于智能型手机上的小型产品。

每一种AI应用(自动驾驶、医疗成像、棋奕游戏)都是调整一款专用AI/ML系统而学习来的结果。每一种应用基本上都有一个AI。因此,下一个问题是:是否可能让AI在学会一件事后,看看它是否能将学到的东西应用于其他类似任务?

Dean说:“提出这个问题是因为我们开始考虑将其用于ASIC设计中的布局与绕线。布局和绕线的规模远远大于下棋游戏。虽然问题的规模更大,但却没有像下围棋时一样清楚的目标。”

Google为布局与绕线建立了一个学习模型,然后着手确定该工具是否可以通用化推广。它能从一个设计上学到知识并应用于前所未有的新设计中吗?答案很明确是肯定的。

Dean说:“此外,至今的各种尝试都获得了超前的成果。它的成果比人为的好一点,有时甚至更好得多。”

Google采用几个不同模块的测试电路,比较使用ML教自己布局和绕线ASIC设计的AI性能。此外,并在渐进式间隔的额外调整后,比较相同ML与商用工具的性能。(来源:Google Research/ISSCC)

其优点包括在极短的时间内执行布局与绕线。完成这项任务可能需要花费人类专家数周的时间,但ML布局与绕线通常可在24小时内完成相同的工作,而且其布局时的线长通常较短。ML绕线器在自动布局绕线工具方面的表现也十分出色。

Dean说,ML还可扩展到IC设计过程中的其他部份,包括使用ML协助产生测试用例,以更充份地利用ASIC设计验证中的状态空间,也许还可以用ML来改进高层级的综合以达到优化设计。

然而,这对于ML的意义与加速IC设计进度的意义一样重要。如果一个ML可以在一个类别中进行概括(gernralize),那么可以在其他类别中进行概括吗?

“未来的ML模型会是什么样子?”Dean问:“我们可以训练一种模型来概推至相似的任务吗?理想情况下,我们需要一种可以学习完成数千或数百万项任务的模型。”

联发科技(MediaTek)资深副总经理陆国宏谈到了AI如何改变几乎与Internet连接的有事物,同时,人工智能物联网(AIoT)将从数十亿台装置迅速发展,预计到2030年,全球将有3,500亿台连网装置。

AI之所以走向边缘,部份原因在于其能力所及,其他原因还包括为了减轻数据中心日益增加的处理负载、让网络流量最小化等需求,以及某些应用需要使用本地处理或最适合于与本地处理搭配使用。

本地处理必须快速、专为AI运算而设计,而且还必须极其节能。

这些本质上是新的处理器类别。陆国宏称其为AI处理单元(APU),有的人则称其为神经处理单元(NPU)、大脑处理单元(BPU)等名称。他说,例如,一个APU可能不如CPU灵活,但由于是专用的,所以APU能以更低55倍的功率加速20倍之多。

陆国宏表示,APU开发人员正开发以3TOPS/Watt实现1TOPS性能的装置。他相信以10TOPS/W达到10TOPS性能是可以实现的,而且最终可能以30TOPS/W的速度达到100TOPS运算效能。

联发科研究人员也在ISSCC上发表另一篇论文,提出“以7奈米5G智能型手机SoC为多功能AI应用实现3.4~13.3TOPS/W

3.6TOPS双核心深度学习加速器”(3.4 to 13.3TOPS/W 3.6 TOPS Dual-Core Deep Learning

Accelerator for Versatile AI Applications in a 7nm 5G Smartphone SoC.)

这毕竟是7奈米(nm)技术。随着摩尔定律(Moore’s Law)的曲线进展到较小的制程节点,至少要再前进一步,例如从目前的7nm到5nm,才可能提高性能。陆国宏认为摩尔定律仍然适用。

然而,也不是没有限制。晶体管的数量随着整合度的增加而增加,并继续遵循经典的摩尔定律曲线,“但每晶体管成本却并未遵循这一规则。”。此外,由于芯片设计的复杂性以及制程步骤变得越来越复杂,导致先进装置的成本飞涨,从而使较小的公司无法导入新技术制程,更别提还有产量问题了。

陆国宏说,解决其中许多问题的常见方案是采用像小芯片之类的技术。他说:“这可能比摩尔定律的表现更好。”但无论是小芯片还是其他架构方法,都意味着在互连方面的挑战。

Imec高速模拟RF计划经理Nadine

Collaert更进一步探讨这场会议的主题,包括如何解决分离裸晶的必要,以及为未来的芯片找到可替代的结构和架构。她称此为系统技术协同优化(system

technology co-optimization或STOC)。

她解释说,摩尔定律可能持续多年,但是微缩CMOS越来越困难。她用FinFET、奈米片等越来越复杂的组件结构示例来说明,这些组件确实都有助于在芯片级进一步实现CMOS微缩。

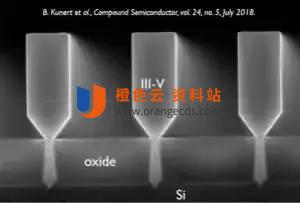

Imec展示可在SOI基底上以奈米脊形生长III-V材料的能力。(来源:Imec/ISSCC)

然而,最终业界还是需要一种新方法。她解释说,“我们相信3D技术是最好的方法。这包括使用线接合的多芯片封装,甚至是在组件级,也可以与其他标准单元进行精细连接。”

如果要搞清楚哪一种技术可用,必须根据可用选件的属性来匹配系统要求。“这将是一个复杂的过程,”Collaert说,而且将会对于EDA供货商带来压力,要求其提供可让设计人员能够权衡其选择的工具。

特别是无线通信系统的前端模块挑战更大。“通常,这些都是最多样化的系统——许多不同组件各自采用不同技术,而且随着使用更多的天线、功率放大器(PA)和滤波器,还会变得更复杂。”

业界正朝着更高的频率和更高的效率迈进。选择之一是将III-V材料(例如GaN和SiC)与CMOS结合使用,以获得两种材料的优势。这可以透过3D整合来完成,她举例说像是在绝缘上覆硅(SOI)基底上生长具有III-V材料的3D奈米脊等,“但这还有待执行很多工作才能实现。”

至于内存?Collaert说:“诸如AI和ML等新应用正推动开发蓝图进展。”这些应用需要快速存取内存。“目前业界开始关注于内存中运算,但随着逻辑和内存之间的距离越来越近,当然更重要的就是采用3D封装。”

未来,在先进应用中采用快闪记体(Flash)将可堆栈更多层。此外,还必须改善在这些内存中的信道电流。“为此,我们必须研究通道迁移性,这又意味着必须研究III-V材料。”同时,透过扩展来研究将硅层与III-V材料层堆栈在一起的3D架构。

而在DRAM方面,电容正从圆柱状逐渐成长为支柱状,这是迈向3D之路的另一种改变。其他内存选项包括用于替代快取的磁性内存和3D储存级内存。Collaert指出,Imec展示了一种垂直铁电场效晶体管(FeFET),但目前正进行更多研究中。

她说,这些内存的发展都是在ML架构下进行的。AI正在蓬勃发展,其中许多都在云端,但由种种原因正准备将其移到边缘,从而节省部份能耗。”Imec认为可能达到10,000 TOPS/W的效能。

“微缩仍在持续中。一切都还没结束呢!”她总结说:“新的内存可能还不在开发蓝图的规划中,但可能会在ML中扩展应用。”

IBM Research总监Dario Gil为此次大会总结了“下一步路在何方”,他说这正是广义的AI之路,而且几乎可以肯定将在量子计算机上实现。此外,他并强调最大的好处可能来自于搭配位(数字处理)、神经元(AI)和量子位(量子运算)的互补使用。

他指出,IBM在2016年开放了第一台量子计算机的云端访问权限,现在可以存取15台量子计算机了,包括其最新的53量子位的量子计算机。

(原文发表于ASPENCORE旗下EDN姐妹媒体EETimes,参考链接:All Processing Bends Toward AI ,编译:Susan Hong)

他首先简要介绍AI和ML的历史,从1995年机器如何学习玩西洋棋开始,到让机器学会在棋赛中脱颖而出,现在已经可以在《星海争霸》(StarCraft)等复杂的视讯游戏取得斐然成绩。ML还被用于医学成像、机器人技术、计算机视觉、自动驾驶车、神经科学、农业以及天气预报等领域。

其优点包括在极短的时间内执行布局与绕线。完成这项任务可能需要花费人类专家数周的时间,但ML布局与绕线通常可在24小时内完成相同的工作,而且其布局时的线长通常较短。ML绕线器在自动布局绕线工具方面的表现也十分出色。

人工智能物联网(AIoT)

系统技术“协同优化”

然而,最终业界还是需要一种新方法。她解释说,“我们相信3D技术是最好的方法。这包括使用线接合的多芯片封装,甚至是在组件级,也可以与其他标准单元进行精细连接。”

量子运算

共 1 条

- 1

64问题数 49回答数